Engineering researchers at North Carolina State University in Raleigh developed two techniques to help maximize performance of multi-core computer chips by allowing them to retrieve data more efficiently. Professor Yan Solihin of NC State’s engineering department and former doctoral student Fang Liu will present their results next month at the International Conference on Measurement and Modeling of Computer Systems in San Jose, California.

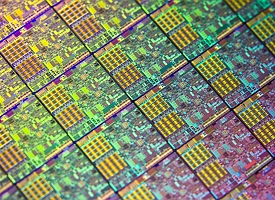

Multi-core chips are designed to make computers run faster, with each core on a chip serving as its own central processing unit. But each core needs to retrieve data from memory that is not stored on its chip. With more of these chips and more cores inside today’s computer systems, the bandwidth available for these data retrievals can get more and more congested.

As designed, multi-core processing chips use a technique called pre-fetching that tries to compensate for this condition. Pre-fetching predicts the data needed by the processor, grabs the data from memory, and stores the data in a separate compartment called a cache. If the prediction is accurate and caching process works, system performance improves. If the prediction is wrong, however, the available bandwidth gets clogged with the wrong data, resulting in slower rather than faster performance.

Solihin and Fang Liu developed two techniques to deal with the problem. The first technique involves more precise and granular bandwidth allotments for each core. Some cores need to retrieve more data than others and need thus more bandwidth. The researchers calculated from the chips’ hardware counters the data needs on each chip to determine the cores’ bandwidth criteria. “By better distributing the bandwidth to the appropriate cores,” Solihin says, “the criteria are able to maximize system performance.”

The second technique uses another set of criteria proposed by the researchers that determine when to use pre-fetching to boost performance. The flip side of this approach indicates when pre-fetching is likely to slow things down and should be avoided. Like the first technique, this method uses data from the chips’ hardware counters. The engineers believe these criteria can help chip manufacturers make multi-core chips operate more efficiently, since each of the individual cores could turn pre-fetching on or off as needed.

With both sets of criteria, the researchers found they could boost multi-core chip performance by 40 percent, compared to multi-core chips that do not pre-fetch data. They also found a 10 percent increase in performance over multi-core chips that always pre-fetch data.

Read More: Engineers Develop Improved Computer Memory Device

* * *

RSS - Posts

RSS - Posts

[…] Read more: Computer Engineers Boost Multi-Core Chip Performance […]

[…] Read more: Computer Engineers Boost Multi-Core Chip Performance […]

[…] Computer Engineers Boost Multi-Core Chip Performance […]